ETRI, 日기술과 비교해 전력 95% 절감 공정 개발

9단계 공정 3단계로 획기적으로 줄이는데 성공

한국전자통신연구원(ETRI) 제공

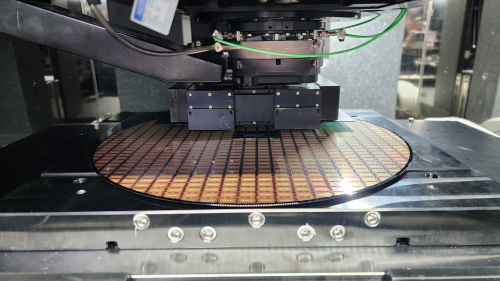

ETRI 자체 개발한 신소재를 적용한 95% 절전 첨단 반도체 칩렛 패키징 공정

한국전자통신연구원(ETRI) 제공

한국전자통신연구원(ETRI) 제공

한국전자통신연구원(ETRI) 저탄소집적기술창의연구실 연구팀은 자체 보유한 나노 소재 기술을 이용해 반도체 공정에 필요한 신소재를 개발했다고 28일 밝혔다. 이번 기술은 일본이 보유한 기술과 비교해서도 95% 전력 절감이 가능하며 공정 단계도 기존 9단계에서 3단계로 줄일 수 있다.

패키징 기술은 반도체 후공정에 해당하는 것으로 웨이퍼로 만들어진 집적회로 소자를 개별로 분리해 모듈로 제작하는 과정이다.

지금까지 첨단 반도체 패키징 공정에 주로 일본 소재를 사용했는데 공정이 9단계이기 때문에 복잡하고 다양한 장비 사용으로 전력 소모가 많고 유해 물질 배출 등 단점이 많았다.

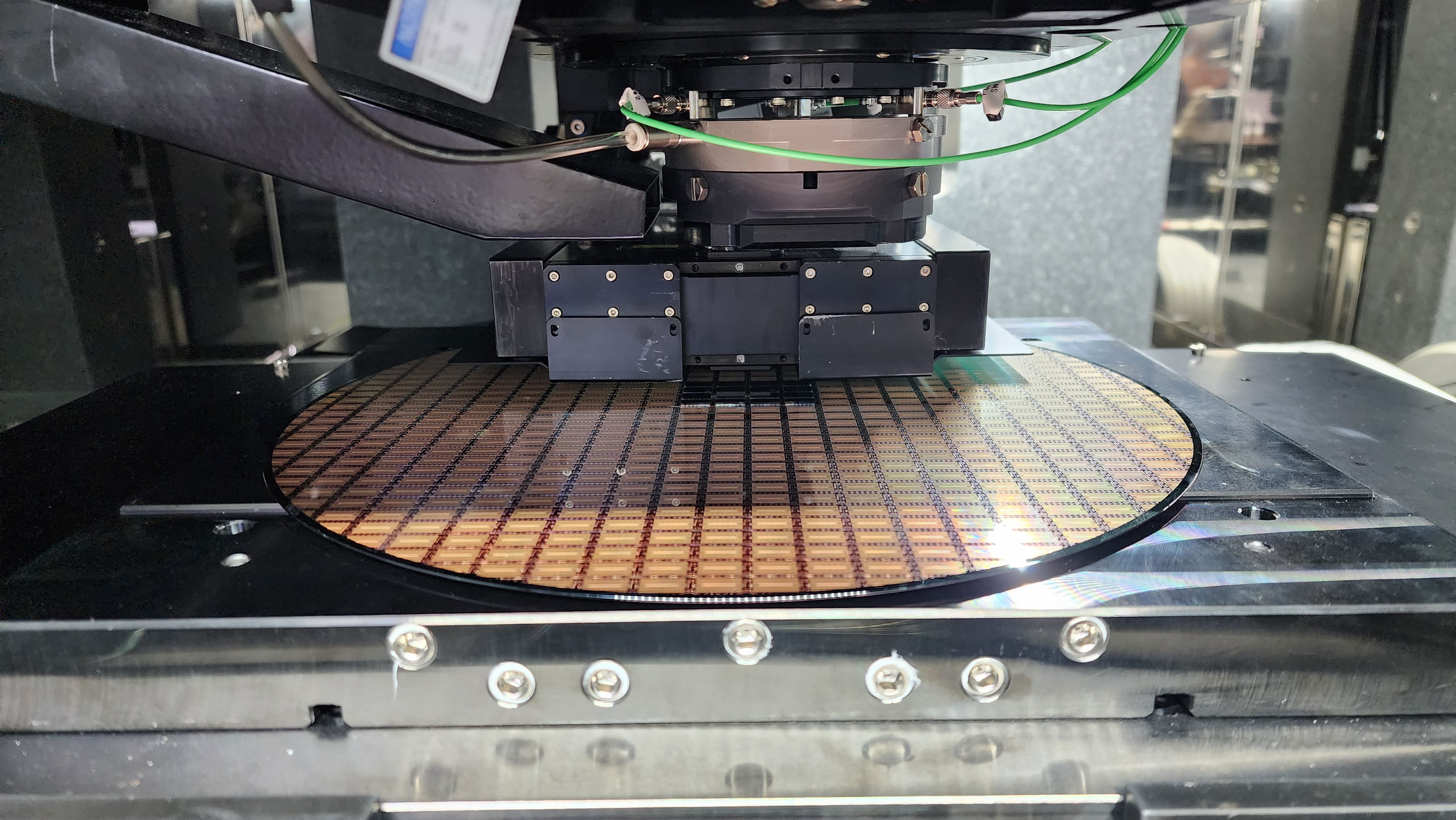

이번에 개발한 기술 공정은 반도체 웨이퍼에 비전도성 필름(NCF)을 붙인 뒤 타일처럼 생긴 칩렛에 1초 정도 면(面) 레이저를 조사해 경화하는 총 3단계로 이뤄진다.

연구팀이 개발에 성공한 핵심 신소재는 고분자 필름으로 만들었다. 10~20㎛(마이크로미터) 두께의 에폭시 계열 소재에 환원제 등이 첨가된 나노소재이다. 여기에 레이저를 조사하면 반도체 후공정인 패키징 단계에서 세척, 건조, 도포, 경화 등이 한 번에 해결된다.

지금까지는 웨이퍼에서 분리한 칩을 보드에 붙여 한 개씩 잘라 쓰는 방식이었는데 이번 기술 덕분에 칩렛을 웨이퍼 기판에 타일 붙이듯 직접 찍어 붙이는 것이 가능해졌다.

ETRI 제공

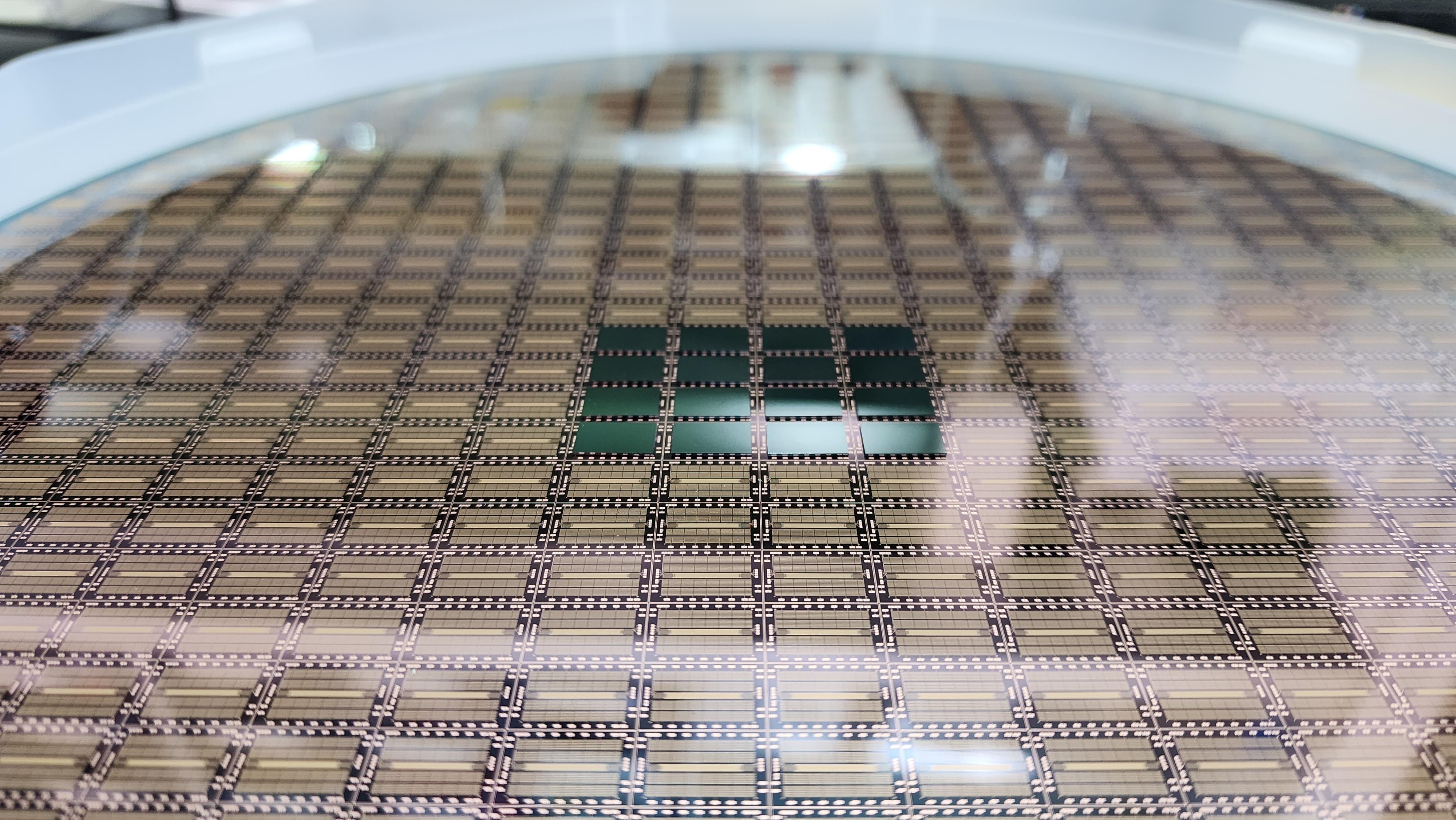

95% 절전 첨단반도체 칩렛 패키징 공정을 적용한 300㎜ 웨이퍼에 집적된 칩렛

ETRI 제공

ETRI 제공

이번 기술은 미국 마이크로 LED 관련 스타트업과 세계적인 파운드리 회사에서 공정성과 신뢰성 평가를 받고 있다. 우수 평가 시 3년 이내에 상용화가 가능할 것으로 전망된다.

최광성 ETRI 창의원천연구본부 저탄소집적기술창의연구실장은 “그동안 첨단 반도체 패키징과 마이크로 LED 디스플레이 분야는 일본 소재와 장비 기술에 대한 의존도가 높았다.”라면서 “기술 격차가 커서 자립화가 쉽지 않은 상황이었는데 저전력, 친환경이라는 새로운 시장의 요구에 연구진의 성과가 답해 원천기술의 상용화가 기대된다”라고 말했다.