패키지 기판 시장 2028년 8조원 연평균 14% 성장

반도체 미세화 한계 극복 위한 패키지 솔루션 중요

멀티 패키지 추세에 따른 기판 기술 고도화 요구

딥앤이지테크

기업들은 급변하는 시장 상황과 기술에 맞춰 국경 없는 경쟁을 펼치고 있습니다. 이미 우리의 일상에도 깊숙이 들어온 첨단 기술과 이를 이끄는 빅테크의 소식을 흥미롭고, 이해하기 쉽게 풀어드립니다.

최근 인공지능(AI) 반도체 시장이 뜨거워지면서 고집적 반도체 칩을 메인보드와 연결하는 고부가 반도체 패키지 기판에 관한 관심도 높아지고 있습니다. 시장조사업체인 프리스마크에 따르면 반도체 기판 시장 규모는 2024년 4조 8000억원에서 2028년 8조원으로 연평균 약 14%로 지속 성장할 것으로 예상합니다.

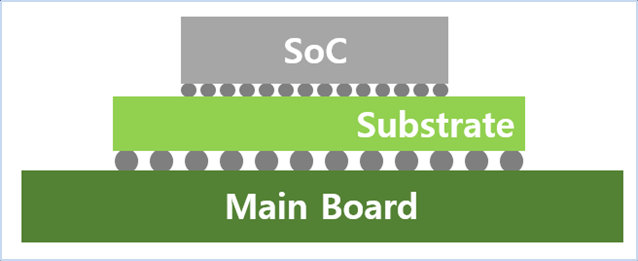

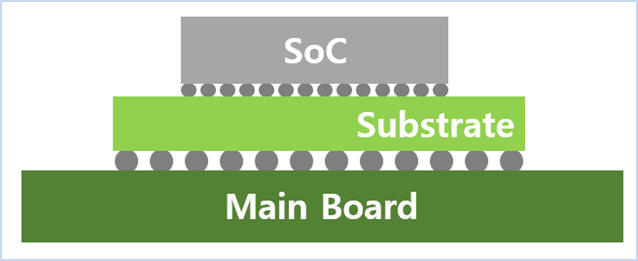

반도체 기판은 반도체와 메인 기판 간 전기적 신호를 전달하고 반도체를 외부 충격 등으로부터 보호해주는 역할을 합니다.

흔히 반도체 칩을 우리 몸의 두뇌에 비유한다면 반도체 기판은 뇌를 보호해주는 뼈와 뇌에서 몸으로 전달하는 정보를 각 기관에 연결해 전달하는 신경과 혈관에 비유할 수 있습니다.

반도체 칩은 메인 기판과 서로 연결되어야 하는데 메인 기판의 회로는 반도체보다 미세하게 만드는 게 불가능합니다. 반도체 칩의 단자 사이 간격은 100㎛(마이크로미터, 0.001㎜)로 A4용지 두께 수준이지만 메인 기판의 단자 사이 간격은 약 350㎛로 4배 정도 차이가 나기 때문입니다.

이 때문에 반도체 칩과 메인 기판 사이를 연결해 주는 것이 바로 반도체 기판의 역할입니다.

삼성전기 제공

반도체 기판의 역할.

삼성전기 제공

삼성전기 제공

반도체 기판 중 하나인 ‘플립칩 볼 그리드 어레이’(FCBGA)는 고집적 반도체 칩과 기판을 ‘플립칩 범프’로 연결해 전기 및 열적 특성을 높이는 패키지 기판입니다. 주로 PC와 서버, 네트워크, 자동차용 중앙처리장치(CPU), 그래픽처리장치(GPU)에 사용되고 있습니다.

반도체 업계에서는 AI뿐 아니라 로봇, 메타버스, 자율주행 등 반도체 성능 향상에 대응할 수 있는 기판 기술에 주목하고 있습니다. 특히 빅데이터와 AI에 적용되는 FCBGA는 대형화, 층수 확대, 미세 회로 구현, 소재 융·복합화 등 높은 기술력이 요구되는 제품입니다.

국내 부품기업인 삼성전기도 지난달 글로벌 반도체 기업인 AMD와 고성능 컴퓨팅(HPC) 서버용 FCBGA 공급 계약을 맺고 제품 양산을 시작했다고 밝힌 바 있습니다.

서버용 FCBGA는 반도체 기판 중에서도 기술적으로 어려운 제품입니다. 전 세계에서 하이엔드급 서버용 기판을 양산하는 글로벌 업체도 일부에 불과하다고 합니다.

서버용 CPU와 GPU는 연산 처리능력과 연결 신호 속도 향상 등 고성능화에 대응하기 위해 하나의 기판 위에 여러 반도체 칩을 한꺼번에 담아야 합니다.

그 때문에 서버용 FCBGA는 일반 PC용 FCBGA보다 기판 면적은 4배 이상 크고, 층수도 20층 이상으로 2배 이상 많습니다.

삼성전기 제공

삼성전기 반도체 패키지 기판.

삼성전기 제공

삼성전기 제공

과거 반도체가 기판 위에 반도체 칩이 하나 올라가는 단순한 구조였다면 최신 반도체는 성능을 높이기 위해 회로의 미세화가 진행되고 트랜지스터 개수도 기하급수적으로 늘어나고 있습니다.

극자외선(EUV) 공법 등 미세화 기술이 개발되고 있지만 미세화 기술 성장 한계와 고가 설비 도입 등으로 인한 공정비용 상승으로 반도체 원가가 높아지면서 패키지 기술과 같은 후공정에서 반도체 성능 향상과 원가를 낮추려는 노력이 이어지고 있습니다.

최근에는 반도체 칩 자체를 잘 만드는 것만큼이나 잘 만들어진 제품을 조합해서 어떻게 구성하느냐 하는 멀티 패키지 기술 영역이 중요해졌습니다.

즉, 패키지 전체의 성능을 끌어올리기 위해 여러 가지 반도체 칩을 반도체 기판에 올려 기능을 향상한 멀티 패키지 형태의 제품들이 나오고 있습니다.

많은 칩이 제대로 작동하기 위해선 기판의 회로 패턴은 더 미세화되고 기판 면적도 커지고 층수도 늘어나는 등 반도체 기판의 기술 고도화가 요구되고 있습니다.

삼성전기는 반도체 기판 분야에서 기술력을 유지하기 위해 1조 9000억원에 달하는 대규모 투자를 통해 부산과 베트남 신공장을 첨단 하이엔드 제품 양산기지로 운영하고 있습니다.

삼성전기는 2022년 10월 국내 최초로 서버용 FCBGA 양산에 성공한 이후 2026년까지 서버, AI, 전장, 네트워크 등 고부가 FCBGA 제품 비중을 50% 이상 확대한다는 계획입니다.

삼성전기 제공

삼성전기 패키지 개발팀장 황치원 상무가 반도체 패키지 기판을 소개하고 있다.

삼성전기 제공

삼성전기 제공

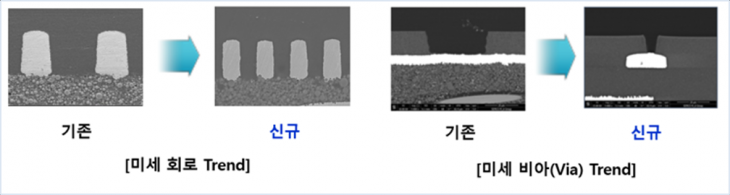

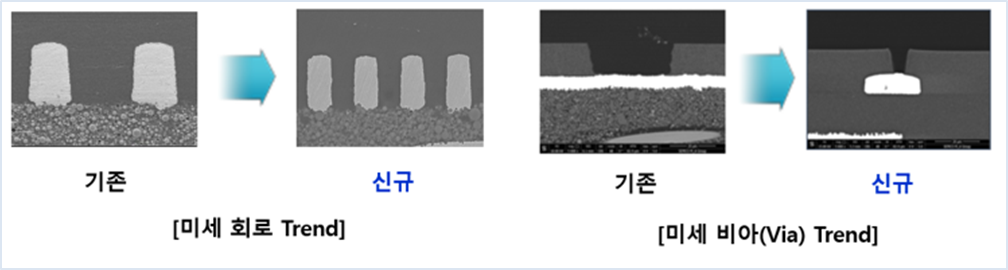

반도체 기판을 만들기 위한 핵심 기술은 미세 가공 기술과 미세 회로 구현에 있습니다. 전자기기의 기능이 많아질수록 필요한 부품이 많아지듯이 반도체 칩의 신호 전달에 필요한 회로도 많아지고 더 복잡해집니다. 한정된 기판 면적 안에 많은 회로를 만들어야 하므로 한 면으로도 부족해 4층, 6층, 8층, 10층 등 여러 층으로 만들게 됩니다.

이때 층간에도 회로가 연결되어야 하므로 구멍을 뚫어 전기적으로 연결하기 위한 도금 과정을 거치게 됩니다. 각 층을 연결해주는 구멍을 ‘비아’(Via)라고 하는데 일반적으로 80㎛ 크기의 면적 안에 50㎛의 구멍을 오차 없이 정확히 뚫어야 하는 만큼 정교한 가공 기술력이 필요합니다.

삼성전기는 A4용지 두께의 10분의 1 수준인 10㎛ 수준의 비아를 구현할 수 있는 미세 비아 형성 기술을 가지고 있습니다.

전기신호가 지나가는 길인 회로는 단자가 많아지고 연결해야 할 신호가 많아지면서 회로 선폭과 간격도 미세화되고 있습니다.

회로 제작 과정은 원하는 회로 두께만큼을 도금한 후 남는 부분을 코팅한 다음 화학 작용인 ‘에칭’을 통해 필요한 회로를 형성하게 됩니다.

삼성전기 제공

미세 회로 Trend와 미세 비아(Via) Trend 비교.

삼성전기 제공

삼성전기 제공

일반적으로 회로 폭과 회로 간 간격은 8~10㎛ 수준의 얇은 선폭을 구현해야 합니다. 삼성전기는 머리카락 두께의 20분의 1인 5㎛ 이하 수준의 회로 선폭을 구현할 수 있는 미세회로 형성 기술을 보유하고 있습니다.

삼성전기는 110㎜ 이상의 초대면적화 기술과 26층 이상의 초고층화 기술, 수동소자 부품을 패키지 기판 내에 내장하는 기술을 확장해 반도체의 성능을 배가시키는 EPS 기술 등 차세대 반도체 기판 시장에서 요구하는 기술을 확보해 고객과의 협력을 강화하고 있습니다.

삼성전기 관계자는 “최근 AI 기술 등에 의한 고성능 반도체 수요가 늘어나면서 FCBGA 수요도 증가할 전망”이라며 “국내 최초 서버용 FCBGA 양산 업체로써 차세대 기판 개발과 반도체 기판 사업 강화에 집중하고 있다”고 강조했습니다.